Большинство САПР использует два способа проектирования интегральных микросхем: коннективистский (метод обеспечения связанности) и геометрический.

- Коннектевистский метод используется в каждой схемотехнической САПР: вы размещаете компоненты и рисуете соединительные проводники. Компоненты останутся соединенными, даже если их перемещать по полю проекта.

- Геометрический метод используется в большинстве топологических систем проектирования интегральных микросхем (ИС): "закрашенные" полигоны распологаются в разных слоях для формирования масок, необходимых для изготовления чипа.

Electric совсем другой , поскольку использует связанность для всего проекта, включая топологию ИС. Это означает, что вы располагаете компоненты (МДП транзисторы, котнакты и т.д.) и рисуете проводники (металл1-2, поликристаллический кремний и т.д.) для их соединения. На экране отображается реальная геометрия, но это означает также и сохранение связанности.

Проектирование топологии ИС с обеспечением связанности дает много преимуществ:

Никакой экстракции узла (No node extraction). Экстракция узла - это не отдельный, подверженный ошибкам шаг. Вместо этого, обеспечение связанности - это легко доступная часть описания топологической схемы. Обеспечение связанности ускоряет все схемотехнические операции, включая моделирование, проверки layout-versus-schematic (LVS) и правильности принципиальной электрической схемы проекта (electrical rules checkers).

- Нет геометрических ошибок. Сложные компоненты не состоят из несвязанных геометрических частей, которые могут перемещаться независимо друг от друга. В системах прорисовки (paint systems), вы можете случайно отодвинуть область затвора от транзистора, таким образом удаляя транзистор. В Electric транзистор - это единый объект, который не может случайно разрушиться.

- Более эффективное редактирование. Просмотр схемы более эффективен, потому что редактор может показать полную цепь всякий раз, когда ее часть выбрана(выделена). Также, Electric совмещает обеспечение связанности с системой топологических ограничений (layout constraint system), давая редактору мощные инструменты управления. Эти инструменты сохраняют проект связанным, даже если схема модифицируется на разных уровнях иерархии.

- шнструменты становятся интеллектуальней, когда они могуть использовать данные о связанности. Например, модуль контроля правил проектирования DRC (Design Rule Сhecker) знает, когда топология связана и использует различные правила размещения.

- Более простой процесс проектирования. При одновременном создании эл. схемы и топологии, получение корректной LVS-проверки включает в себя много шагов устранения ошибок DRC. Так происходит потому, что извлечение узла должно быть закончено для обеспечения связности топологии ИС, и экстракторы узлов схем не работают тогда, когда правила проектирования нарушены. Так каждый раз, когда проверка LVS находит проблемы, топология должна быть исправлена и DRC опять очищается. С этого момента Electric сможет извлекать связи для LVS без идеального соблюдения правил проекта, первый шаг - это приведение в соответствие топологии и эл. схемы. Далее правила проектирования могут быть очищены без опасности потери соответствия LVS.

- Обычный пользовательский интерфейс. Одна САПР, с единым пользовательским интерфейсом, может быть использована для создания как топологии, так и эл. схемы. В Electric тесно интегрированы процессы рисования отдельных схем и LVS-инструмент для их сравнения.

Недостатки САПР топологии ИС, основанных на конективистском подходе также известны:

- Они отличаются от всех остальных и требуют переподготовки. Это действительно так, но многие инженеры переучились и нашли их стоящими. Пользователи, которым хорошо знакома геометрическая компоновка топологии ИС обычно обучаются дольше и тяжелее. Electric подходит для тех кто не имеет опыта проектирования ИС.

- Требует дополнительных действий со стороны пользователя для обеспечения связности. В то время как это может быть верным на начальных стадиях проектирования, в целом это не так. Так получается потому, что используя связность на первых стадиях проектирования вы помогаете системе находить проблемы в будущем. Кроме того, Electric имеет мощный инструментарий для автоматического управления связностью.

- Проектирование происходит не в режиме точной визуализации (WYSIWYG - what-you-see-is-what-you-get) потому что объекты, которые соприкасаются на дисплее могут не быть реально соединенными. Electric оснащен инструментами, гарантирующими то, что связанность создана должным образом.

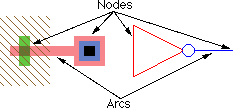

Electric обрабатывает все типы проектирования схемы путем отображения на экране совокупности узлов (Nodes) и дуг, соединненых в цепь. Узлы - электрические компоненты, такие как транзисторы, контакты и логические вентили. Дуги (Arc)- это проводники, которые соединяют два компонента. Порты (Ports) - точки на узлах, к которым подключаются дуги

В рассмотренном примере, узел транзистора имеет три геометрические области на различных слоях: поликремний, активная область, и подложка. Этот узел может быть масштабирован, повернут и изменен иным способом не касаясь размера конкретного слоя. Так происходит потому, что правила для рисования узла запрограммированы в технологии, которая описывает узлы и дуги в терминах конкретных слоев.

Поскольку Electric использует узлы и дуги для проектирования, важно то, что они используются для создания всех соответствующих соединений. Несмотря на то что топология кажется соединенной когда два компонента соприкасаются, проводник обязательно должен быть использован с тем, чтобы указать связь для Electric. Это требует немного больше усилий при проектировании схемы, но это усилие оплачивается сполна многими способами когда Electric понимает вашу схему.

Помимо создания разнообразных электрических цепей, дуги, которые формируют проводники в Electric, могут также удерживать ограничения (constraints). Связь помогает контролировать изменения геометриии - например, жесткая связь скрепляет два компонента в фиксированную конструкцию в то время как остальная часть схемы растягивается. Такие связи распространяются в схеме, даже против иерархических уровней проекта, так, чтобы очень сложные схемы могли разумно управляться.

Ячейка (Cell) - это совокупность узлов и дуг, формирующих описание схемы. Бывают различные виды(представления) ячейки, такие как схематический, топология, пиктограммы, и т.д. Также, каждый вид ячейки может различаться версиями, формированием истории проекта. Кратные(Multiple) виды и версии ячейки организуются в группу ячеек (Cell groups).

Например, ячейка тактового генератора(clock) может состоять из схематического и топологического вида (описания). Схематический вид бывает двух версий: 1(более старая) и 2(более новая). В этом случае группа ячеек тактового генератора содержит три ячейк: топологический вид (называется "clock{lay}"), текущее схематическое представление (называется "clock{sch}") и старое схематическое представление (называется "clock;1{sch}").

шерархия реализуется при помещении одной ячейки в другую (вложенность описаний). Когда это происходит, размещенная ячейка распологается ниже в иерархии, и ячейка в которой размещают - выше. Поэтому, понятие движения вниз по иерархии подразумевает перемещение во вложенный экземпляр ячейки, а понятие восхождения по иерархии означает переход туда где размещена ячейка. Обратите внимание, что экземпляры ячейки - это фактически узлы, точно такие же как элементарные транзисторы и вентили. Определяя внешние связи (exports) внутри ячейки, вы делаете их местами соединения, или портами, в экземплярах этой ячейки.

Совокупность ячеек формирует библиотеку, и она представляет собой на диске отдельный файл. Поскольку полная библиотека обрабатывается как отдельный файл, она может содержать завершенную иерархию ячеек. Любая ячейка в библиотеке может содержать образцы других ячеек. Завершенная схема может быть сохранена в отдельной библиотеке, или может быть разбита на множество библиотек.