С помощью команды Write Verilog Deck... меню (Tool / Simulation (Verilog)) Electric может создавать входные файлы для Verilog симуляторов. Далее для получения ".dump" файла вам надо запустить внешний Verilog симулятор, т.к. дистрибутив Electric не включает Verilog симулятор!!!

Для просмотра результата вы можете полученный ".dump" файла считать обратно в Electric. Это можно сделать воспользовавшись командой Plot Verilog VCD Dump... меню (Tool / Simulation (Verilog)). Если имя файла совпадает с именем ячейки, то удобно использовать команду Plot Verilog for This Cell. Результат работы Verilog симулятора представляется в окне цифрового сигнала (подробнее Section 4-2-11).

Перед генерацией Verilog записи, полезно закомментировать схему с помощью добавочного Verilog пояснения и кода, который будет включен в запись. Для добавления Verilog кода, выберите из компонентного меню "Misc." пункт "Verilog Code". Для добавления пояснения - "Verilog Declaration". (подробнее о манипуляциях с текстом см. Section 6-8-1 ).

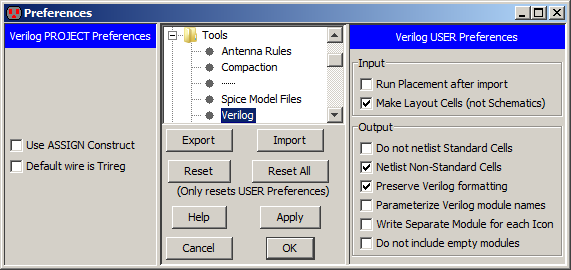

Дополнительные настройки генерации Verilog записи можно найти в Verilog настройках меню (File / Preferences..., "Tools", "Verilog").

Левая сторона - Verilog Project Preferences, у которого есть два средства управления:

"Use ASSIGN Construct" позволяет Вам выбирать, использовать ли Verilog, "присваивают" конструкцию.

"Default wire is Trireg", позволяет Вам управлять типом объявления Verilog, которое будет использоваться для проводников ("wire" по умолчанию, "trireg" если отмечено). Отметьте, что это может быть переопределено командой Set Verilog Wire (меню Tools / Simulation (Verilog)).

Другое свойство, которое может быть присвоено транзисторам, является их мощность. Команда Weak (в меню Tools / Simulation (Verilog) / Transistor Strength) устанавливает маломощный транзистор. Команда Normal восстанавливает транзистор нормальной мощности.

Все еще больше управления генерации кода для Verilog связано с Пользовательскими настройками Verilog в правой стороне диалогового окна.

"Run Placement after import" указывает, чтобы инструмент Размещение использовался, чтобы организовать компоненты после чтения Verilog (см. Раздел 9-13).

"Do not netlist Standard Cells" пишет netlist, который исключает Standard Cells. Любая ячейка, отмеченная как Standard Cells, будет netlisted только как экземпляр, но никакое определение модуля не будет записано. Это позволяет базируемому моделированию Standard Cells или Static Timing Analysis выполняться на netlist. См. Раздел 3-7-3 для подробностей по этому вопросу.

"Preserve Verilog formatting" сохраняет добавление отступа и другое форматирование текста.

"Parameterize Verilog module names", заставляет генерацию деки Verilog создавать многократные описания ячейки Verilog, когда ячейки параметризованы.

"Write Separate Module for each Icon" запрашивает, чтобы схематические ячейки со значками были записаны многократно в файл Verilog, однократно для каждого изменения значка. Это сохраняет иерархическую структуру схемы, но создает дубликаты модулей.

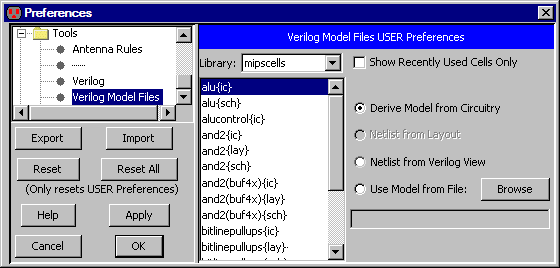

Заключительный набор средств управления Verilog может быть найден в Verilog Model Files Preferences (в меню File / Preferences..., "Tools" section, "Verilog Model Files" tab). Диалоговое окно Verilog Model Files Preferences позволяет Вам управлять, как каждая ячейка должна быть представлена в Verilog.

Значение по умолчанию создает Verilog из фактического содержания ячейки. Если есть эквивалентная топология ячейки, то она также может использоваться (вместо схемного). Вы можете использовать представление "Verilog", которое содержит текст Verilog для такой ячейки. Наконец, Вы можете указать, чтобы использовался внешний файл модели. Эти варианты позволяют Вам создавать свои собственные определения в ситуациях, где полученный Verilog код был бы слишком сложным или неправильным.